2009 Workshop on Dependable and Secure Nanocomputing

## Scaling Effects on Neutron-Induced Soft Error in SRAMs Down to 22nm Process

Production Engineering Research Lab., Hitachi, Ltd. E. Ibe, Fellow, IEEE, H. Taniguchi, Y. Yahagi, K. Shimbo, and T. Toba

### Contents

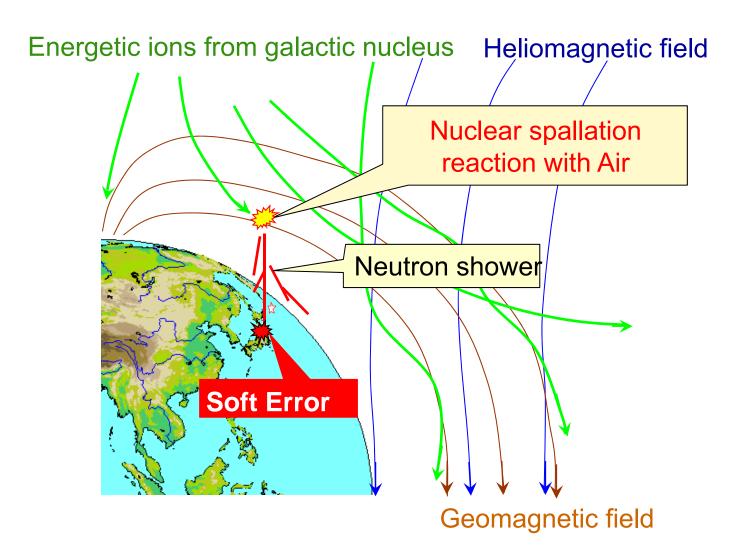

- *1* Fundamentals of Neutron-Induced Soft-Error

- 2 Model Description and Validation

- 3 Predicted Scaling Effects

- 4 Discussions

- 5 Summary

### Contents

- *1* Fundamentals of Neutron-Induced Soft-Error

- 2 Model Description and Validation

- 3 Predicted Scaling Effects

- 4 Discussions

- 5 Summary

All Rights Reserved Copyright © 2007, Hitachi, Ltd.

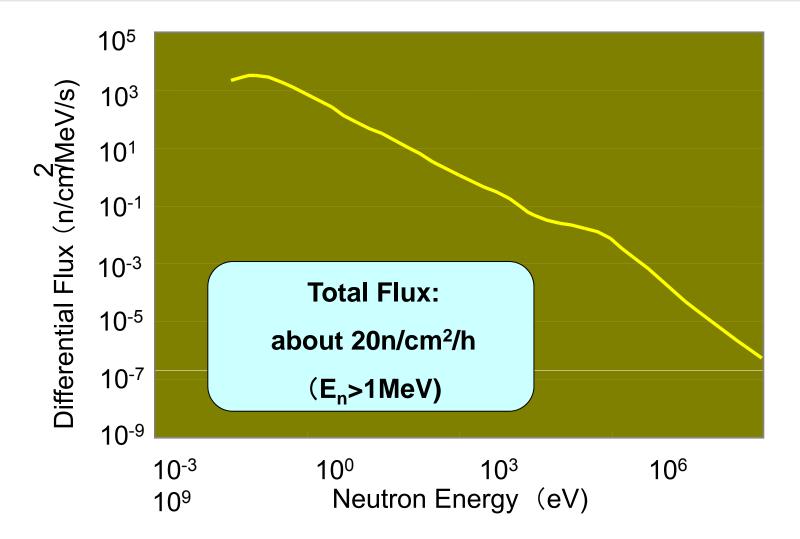

## 2 Estimated Neutron Spectrum in Tokyo\* HITACHI

\*Estimated from the spectrum at the sea level in NewYork (JESD89A,2006)

3

**HITACHI**

Inspire the Next

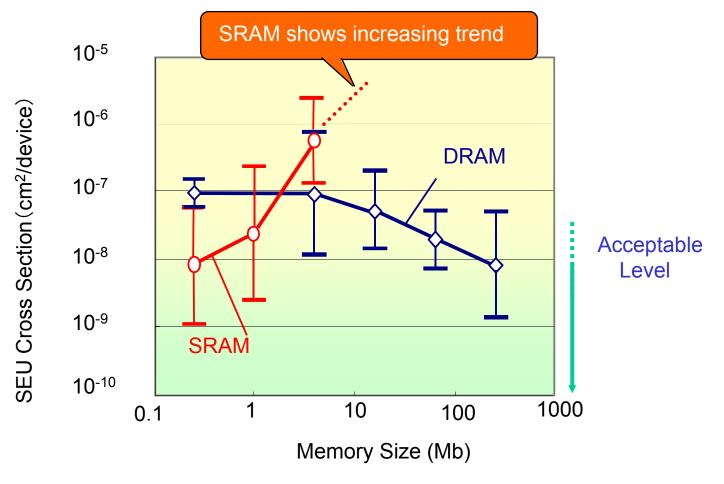

\*SEU Cross Section = Errors/number of incident nucleon

Ibe, E., "Current and Future Trend on Cosmic-Ray-Neutron Induced Single Event Upset at the Ground down to 0.1-Micron-Device," The Svedberg Laboratory Workshop on Applied Physics, Uppsala, May, 3, No.1 (2001).

### Contents

- *1* Fundamentals of Neutron-Induced Soft-Error

- 2 Model Description and Validation

- 3 Predicted Scaling Effects

- 4 Discussions

- 5 Summary

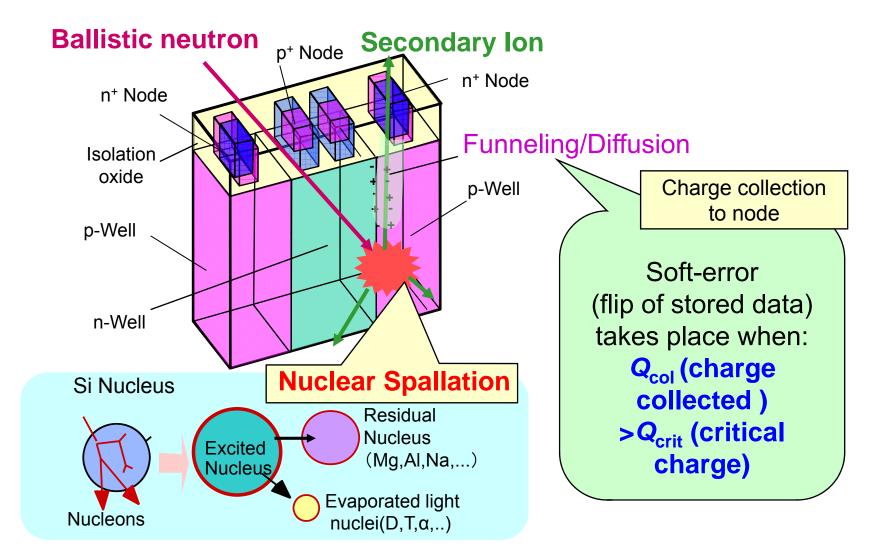

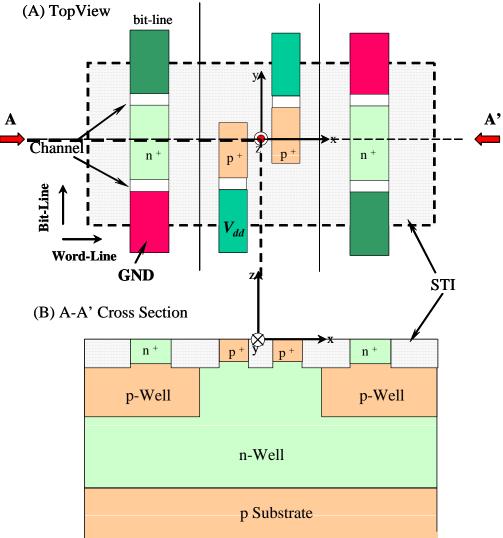

First-principle model for nuclear spallation reaction

- Realistic model of devices (DRAM. SRAM, FF, SESO, ZRAM...)

- in 3D dimensions with storage nodes, interlayer oxide, STI, well,

- depleted zone, deep n-isolation, etc.

- Realistic charge collection models (funneling, drift-diffusion)

- No limit in the number of cells thanks to the Dynamic Cell Shift

- (DCS) model

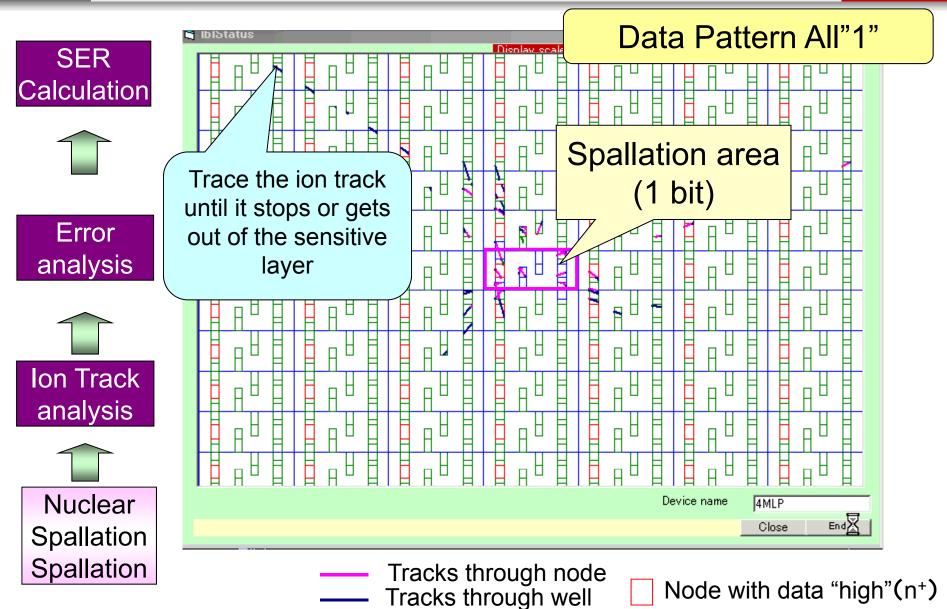

- Any data pattern including AllX(All"1" and All"0") and checkerboard (CB and its compliment)

- Interleaving technique can be implemented, which enables the ECC design.

Any neutron/proton energy spectrum including environmental/ accelerator neutron spectra can be applied from the data base. ....and more

6

### SRAM Model

HITACHI Inspire the Next

All Rights Reserved Copyright © 2007, Hitachi, Ltd.

7

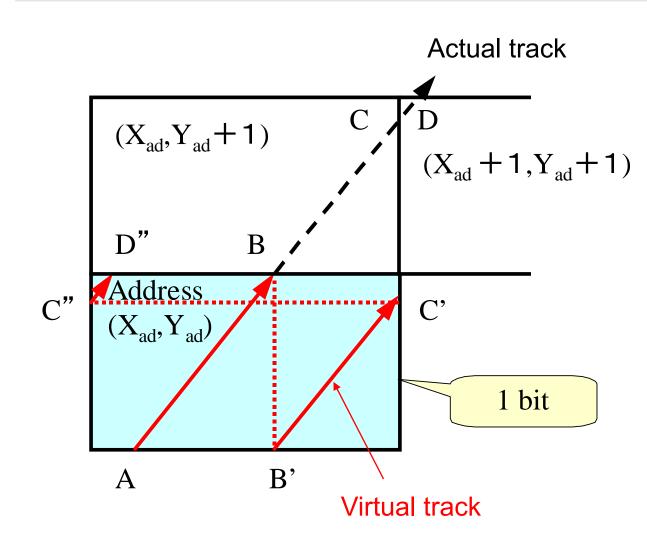

## **DCS Method**

Enables to calculate ion tracks until it stops without any ion range limit.

Utilizes only one physical cell model (Does not make an NxN cell array)

Shifts the ion track parallel when it reaches the cell boundary and the cell physical address is incremented or decremented according to the boundary location.

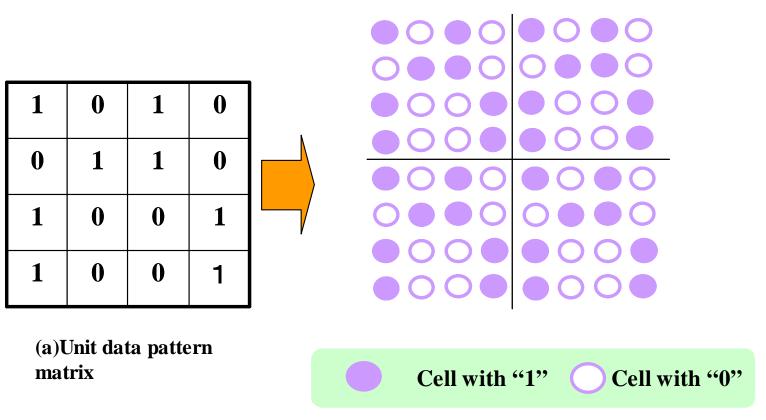

## Data Pattern implementation

(b) Spreading the matrix onto a device

Define unit data pattern matrix including CB and AllX

Virtually spread the matrix onto a device and the data in a cell can be calculated according to the physical address.

TACH

### Display of Part of Cell Array Matrix and Ion tracks

HITACHI Inspire the Next

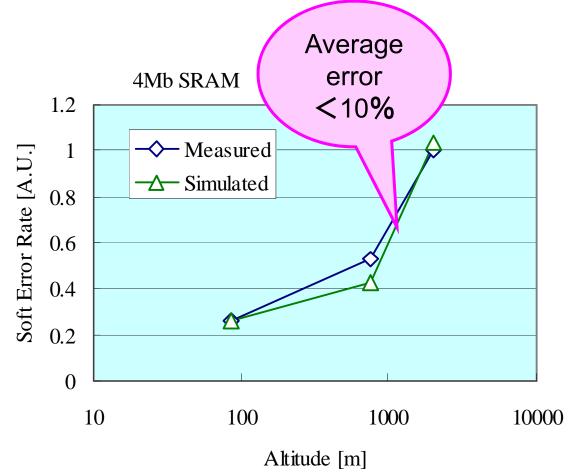

# 10 Validations of the Model

Comparison between measured and simulated SERs in three different locations in Japan

Within 20% error for simulations of experiments in :

-TSL (Uppsala, Sweden)

-CYRIC (Sendai, Japan)

-LANSCE(Los Alamos, USA)

-RCNP(Osaka, Japan)

# 11

# Assumed Road Map

#### Assumptions

Cell area decreases by half for each down-scaling.

Density doubles. Critical charge decreases by half

(In principle, critical charge is in proportion to parasitic capacitance which again in proportion to cell area)

Depth profile does not change

Operation voltage does not change

|             | SRAM property |         |       |  |  |

|-------------|---------------|---------|-------|--|--|

| Design rule | Cell area     | Density | Qcrit |  |  |

| nm          | A.U.          | Mbit    | A.U.  |  |  |

| 130         | 2.1           | 16      | 3.2   |  |  |

| 90          | 1             | 32      | 1.6   |  |  |

| 65          | 0.5           | 64      | 0.8   |  |  |

| 45          | 0.25          | 128     | 0.4   |  |  |

| 32          | 0.125         | 256     | 0.2   |  |  |

| 22          | 0.06          | 512     | 0.1   |  |  |

### Contents

- *1* Fundamentals of Neutron-Induced Soft-Error

- 2 Model Description and Validation

- 3 Predicted Scaling Effects

- 4 Discussions

- 5 Summary

# 13 Major Simulation Results(CB)

| Design rule | SER (      | A.U)     | MCUratio | MCU<br>maximum<br>size | Maximum bit multiplicity |

|-------------|------------|----------|----------|------------------------|--------------------------|

| nm          | per device | per Mbit | %        | bit                    | bit                      |

| 130         | 1          | 1        | 7        | 459                    | 10                       |

| 90          | 2.0        | 1.00     | 14.8     | 14940                  | 16                       |

| 65          | 3.2        | 0.81     | 21.2     | 114170                 | 19                       |

| 45          | 4.4        | 0.55     | 27.2     | 118665                 | 48                       |

| 32          | 6.1        | 0.38     | 38.5     | 1932765                | 52                       |

| 22          | 7.0        | 0.22     | 46       | 463638                 | 175                      |

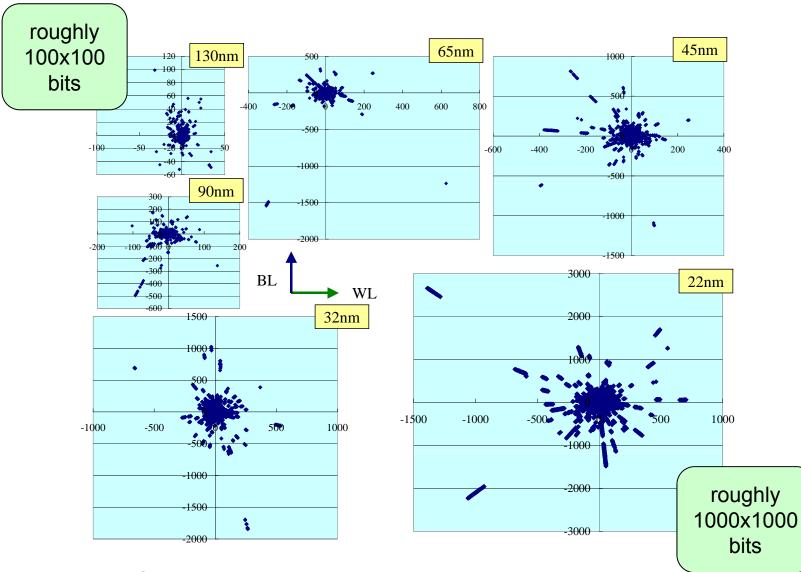

SER /Mbit decreases with down-scaling but SER /device increase x7 from 130nm to 22 nm.

MCU ratio increases x7 from 130nm to 22nm

MCU maximum size (MxN bits rectangular area that includes failed bits) exceed as many as 1Mbits in the extreme case.

Maximum bit multiplicity exceeds as many as 100 bit for 22nm process.

# 14 Spread in Failed Bit Map for All Errors

\*Spallation reaction location is the origin.

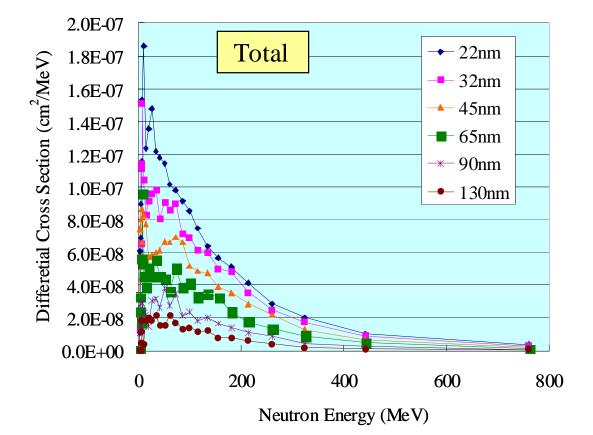

# Shifts in SEU Cross Section

SEU includes SBU(Single Bit Upset) and MCU(Multi Cell Upset).

HITACHI Inspire the Nex

The peak in the cross section curves becomes more apparent and appears at lower energies with down-scaling

The shape of the cross section curves changes from saturation curve (130nm) to exponential-like curves with down scaling

Contribution of lower energy neutron become more significant with downscaling

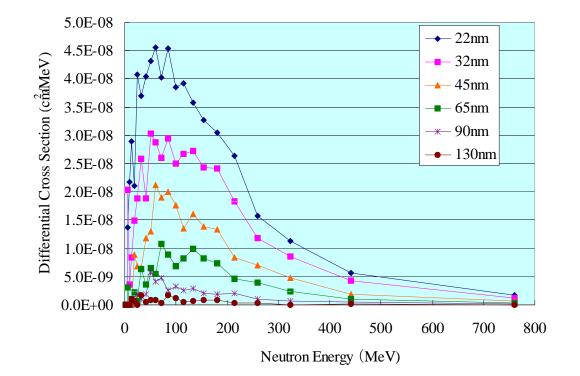

The shape of the MCU cross section curves does not change significantly with the peak location roughly at 60-100MeV.

The shape of the MCU cross section curves is basically exponential-like for the higher neutron energy than about 100MeV.

Comparison with the SEU cross section indicates that SBU is dominant below 100 MeV and become more significant with down-scaling.

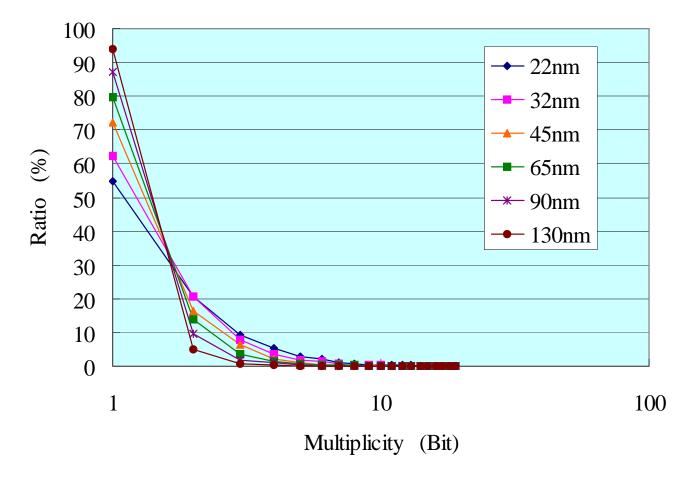

## Shifts in Bit Multiplicity

Bit multiplicity increases with down-scaling

All Rights Reserved Copyright © 2007, Hitachi, Ltd.

HITACHI Inspire the Next

### Contents

- *1* Fundamentals of Neutron-Induced Soft-Error

- 2 Model Description and Validation

- 3 Predicted Scaling Effects

- 4 Discussions

- 5 Summary

| Factor                   | Assumption       | Possible trend       | Influence                   |

|--------------------------|------------------|----------------------|-----------------------------|

| Operation<br>voltage     | constant         | decrease             | Q <sub>crit</sub> ↓<br>SER↑ |

| Depth profile            | constant         | shallower and denser | SER↓                        |

| Gate oxide<br>material   | SiO <sub>2</sub> | HfO<br>(high k)      | Q <sub>crit</sub> ↑<br>SER↓ |

| Inter-layer<br>isolation | SiO <sub>2</sub> | Low-k                | Q <sub>crit</sub> ↓<br>SER↑ |

# 19 Implications for Logic Devices

Increases in MCU bit multiplicity and in MCU size imply that MNU(Multi Node Upset:Multiple faults in nodes in a logic device) takes more often and in wider area.

Increase in MNU may impair radiation-hardened device with redundancy nodes like DICE.

Increase in MNU also implies that logic devices in the vicinity may be failed simultaneouly resulting in impairing redundancy circuits like DMR, TMR and so on.

Nobel radiation hardening techniques have to be developed for logic devices and systems with a large number of logic devices with reasonable speed/power/area overheads. Interactive countermeasures among device/component/system layers will be effective.

## Summary

- Soft-error rates per device in SRAMs will increase x7 from 130nm to 22nm process.

- As SRAM is scaled down to smaller size, soft error rate is dominated more significantly by low energy neutrons (<10MeV)</p>

- The area affected by one nuclear reaction spreads over 1M bits area and bit multiplicity of multi-cell upset become as high as 100 bits and more.

- The discussions are extended to the MNU of logic devices and systems. Development of interactive countermeasures among device/component/system layers is proposed to cope with the real threats in the future.

### Reference

T. Nakamura, M. Baba, E. Ibe, Y. Yahagi and H. Kameyama, Terrestrial Neutron-Induced Soft-Errors in Advanced Memory Devices, World Scientific, 2008

Thank you for your attention!

HITACHI Inspire the Next