The 39th Annual IEEE/IFIP International Conference on Dependable Systems and Networks

June 29-July 2, 2009 — Estoril, Lisbon, Portugal

# Third Workshop on Dependable and Secure Nanocomputing

Organizers:

- Jean Arlat, LAAS-CNRS

- Cristian Constantinescu, AMD

- Ravishankar K. Iyer, UIUC

- Johan Karlsson, Chalmers Univ.

- Michael Nicolaïdis, TIMA

Monday June 29, 2009

### **Program Committee**

Jacob A Abraham Lorena Anghel Davide Appello Vikas Chandra **Yves** Crouzet Giorgio Di Natale Babak Falsafi Richard E. Harper Shubhendu S. Mukherjee Takashi Nanya Jean-Jacques Quisquater Juan Carlos Ruiz García Allan Silburt Arun Somani Janusz Sosnowski Andreas Steininger Alan Wood **Yervant** Zorian

University of Texas, Austin, USA TIMA, Université de Grenoble, France STMicroelectronics, Agrate Brianza, Italy ARM R&D, San Jose, CA, USA LAAS-CNRS, Toulouse, France LIRMM, Montpellier, France EPFL, Lausanne, Switzerland IBM Research, Yorktown Heights, NY, USA Intel Corp., Hudson, MA, USA University of Tokyo, Japan Univ. Cath. Louvain, Belgium Univ. Politécnica de Valencia, Spain Cisco Systems, Ottawa, ON, Canada Iowa State University, Ames, USA Warsaw University of Technology, Poland Vienna University of Technology, Austria Sun Microsystems, Santa Clara, CA, USA Virage Logic, Fremont, CA, USA

Third Workshop on Dependable and Secure Nanocomputing The 39th Annual IEEE/IFIP International Conference on Dependable Systems and Networks

# Program Set up

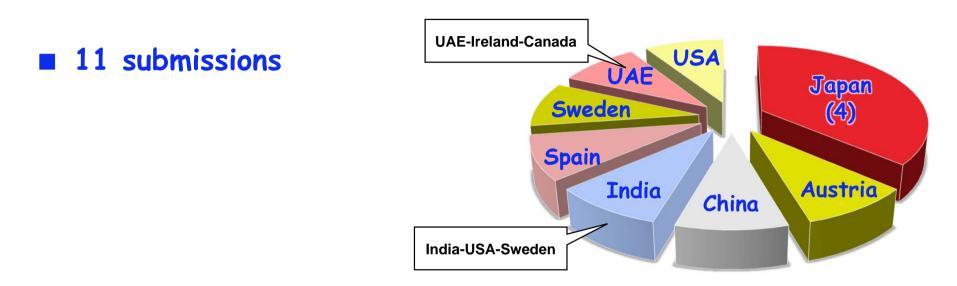

- Each submission reviewed by 4+ PC members

- Selection —> 8 presentations from submitted contributions

- 2 invited talks

#### Program-at-a-Glance

Moderator

| L U                  | nd Invited Talks Jean Arlat                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------|

|                      | Workshop Introduction<br>Vikas Chandra, Cecilia Metra                                                           |

| 10-10:30 Coffee      |                                                                                                                 |

| 2- Reliability       | Issues and AssessmentJohan Karlsson                                                                             |

| 10:30-11:50          | Eishi Ibe, Valeriu Beiu, David de Andres, Scott Bingham                                                         |

| 11:50-12             | Additional Discussion                                                                                           |

| 12-13:30 Lunch       |                                                                                                                 |

| <b>3- Resilience</b> | Enhancement TechniquesMichael Nicolaïdis                                                                        |

| 13:30-14:50          | Tomohiro Yoneda, Daniel Skarin, Pramod Subramanyan, Andreas Steininger                                          |

| 14:50-15             | Additional Discussion                                                                                           |

| 15-15:30 Coffee      | break                                                                                                           |

| 4- Panel and         | ClosingCristian Constantinescu                                                                                  |

| Scaling Tow          | ards Nanometer Size Devices: Issues and Solutions                                                               |

| 15:50-10:20          | <b>Presentations by the panelists</b><br>Jacob Abraham, Valeriu Beiu, Helia Naeimi, Arun Somani, Seongmoon Wang |

| 16:20-17             | Panel discussion and Workshop Wrap up                                                                           |

| 17 Worksho           | p Adjourn                                                                                                       |

Third Workshop on Dependable and Secure Nanocomputing The 39th Annual IEEE/IFIP International Conference on Dependable Systems and Networks

## **About Nanocomputing**

- Nanocomputing describes computing that uses extremely small — or nanoscale — devices (1 nm = 10<sup>-9</sup> m).

- Top Down: MOS device downscaling "More Moore"

- Bottom Up: (Self-)assemblies of nanoelectronics devices "Beyond Moore"

- NanoComputing: The End Not Here Yet, But Coming Soon, Science, Vol. 293. no. 5531, August 2001, p. 787

- The Future of Nanocomputing, George Bourianoff, Intel Corp., Computer, Aug. 2003, pp. 44-53

- Computer Architectures for Nanotechnology: Towards Nanocomputing, Christian Gamrat, CEA/LIST, in Nanoscience, (C. Dupas, P. Houdy, M. Lahmani, Eds), Springer, 2007

- Towards Achieving Reliable and High-performance Nanocomputing via Dynamic Redundancy Allocation, Shuo Wang, Lei Wang, Faquir Jain, ACM J. on Emerging Technologies in Computing systems, Vol.5, no.1, Jan. 2009

5

# ITRS\* Crosscutting Challenge 5: Reliability

Relaxing the requirement of 100% correctness for devices and interconnects may dramatically reduce costs of manufacturing, verification, and test. Such a paradigm shift is likely forced in any case by technology scaling, which leads to more transient and permanent failures of signals, logic values, devices, and interconnects.

Several example issues are as follows. 1) Below 65nm, single-event upsets (soft errors) impact field-level product reliability, not only for embedded memories, but for logic and latches as well. 2) Methods for accelerated lifetime testing (burn-in) become infeasible as supply voltages decrease (resulting in exponentially longer burn-in times); even power demands of burn-in ovens become overwhelming. 3) Atomic-scale effects can demand new "soft" defect criteria, such as for non-catastrophic gate oxide breakdown. In general, automatic insertion of robustness into the design will become a priority as systems become too large to be functionally tested at manufacturing exit.

Potential solutions include automatic introduction of redundant logic and onchip reconfigurability for fault tolerance, development of adaptive and selfcorrecting or self-healing circuits, and software-based fault-tolerance.

\* International Technology Roadmap for Semiconductors — 2008 Update (www.itrs.net)

Third Workshop on Dependable and Secure Nanocomputing The 39th Annual IEEE/IFIP International Conference on Dependable Systems and Networks