# Dependability and Security Challenges in Emerging Technologies

Jacob A. Abraham

University of Texas at Austin

Workshop Panel June 28, 2007

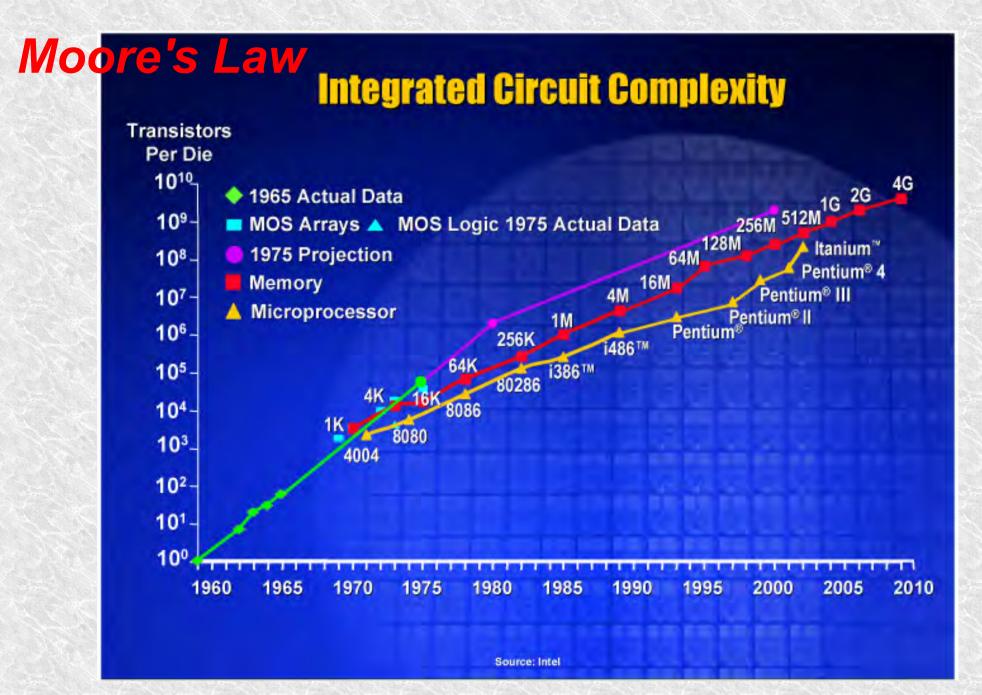

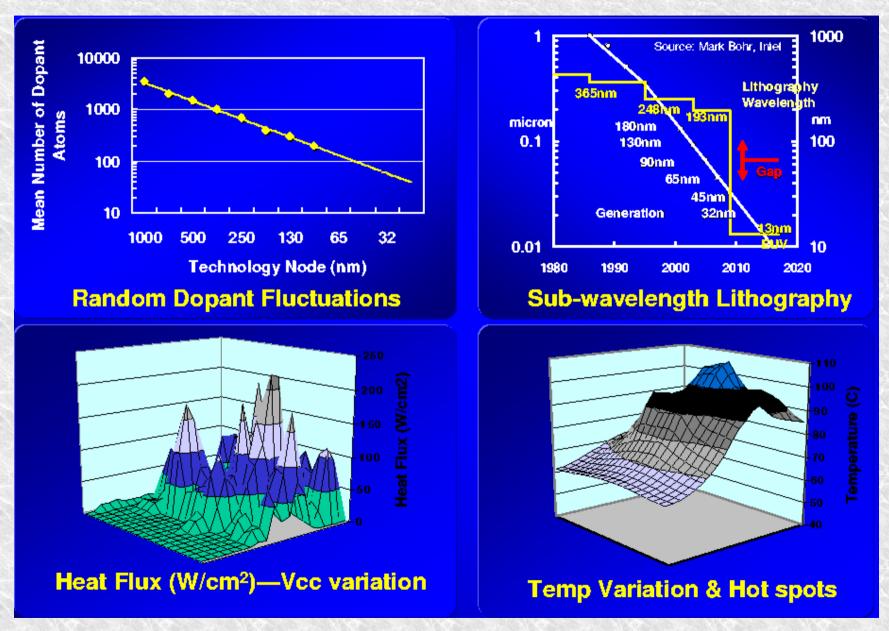

## Nanoscale CMOS Trends

## **Process Variations**

Source: Intel

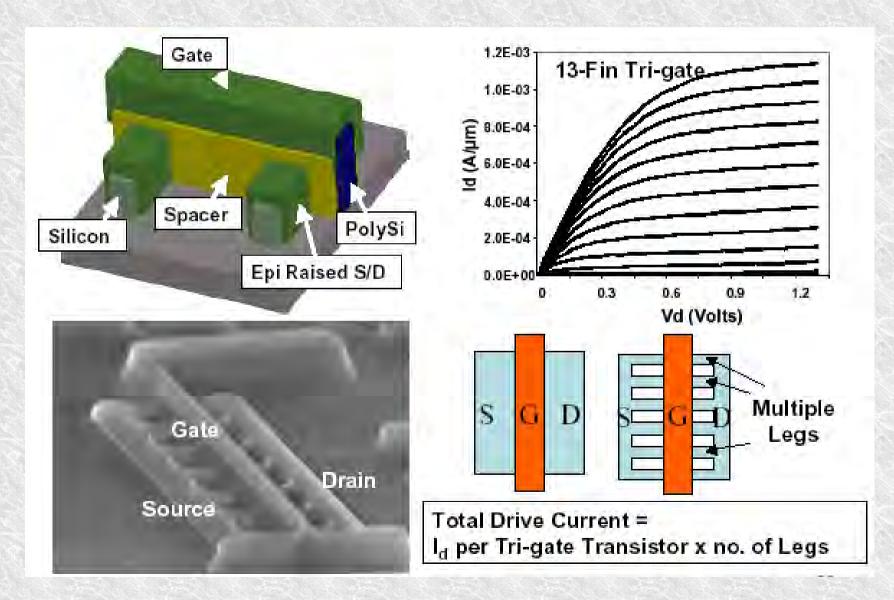

## Nanoscale CMOS Example

#### Fin-FETs

## Effects on Circuits and Systems

- Experiments on chips today show that running some chips at rated speeds produce errors

- Correct operation when running at normal speeds

- Resistive opens (possible in copper interconnect) cause delay defects

- Crosstalk effects could also cause errors

- As technology scales down, chips in the future prone to erroneous operation due to:

- Process variations (soft errors)

- Increasing defects (today's memories are an example)

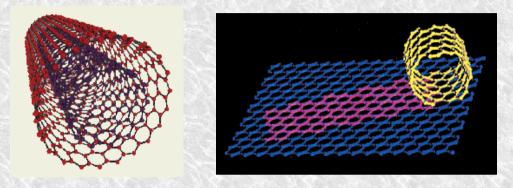

## New Nano Systems

#### **Carbon Nanotubes**

## New Nano Systems

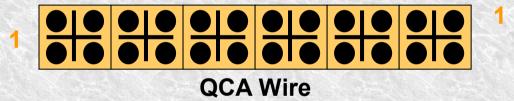

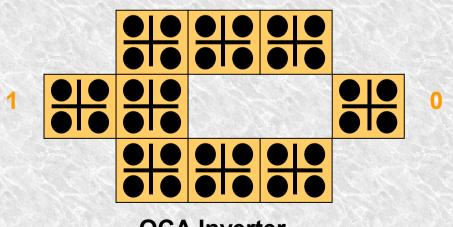

#### **Quantum Devices**

#### Quantum Cellular Automata

Stable

**Unstable**

**QCA** Inverter

## Dealing with Errors

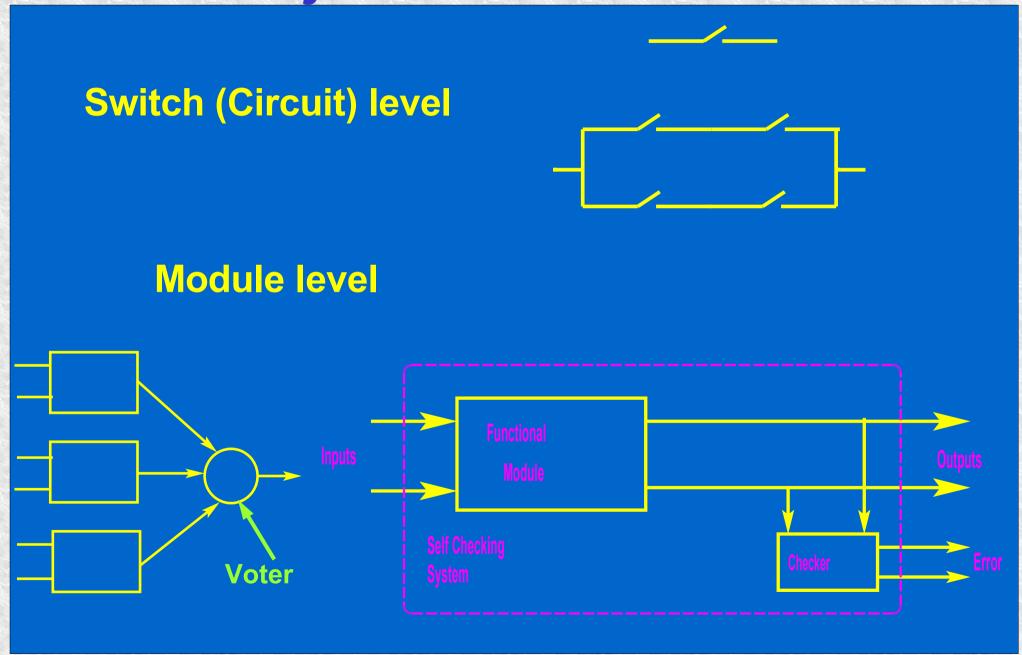

- Redundancy

- Hardware (duplication/retry, triplication)

- Time (recomputation)

- Basic ideas in dealing with errors are not new

- Moore and Shannon, 1956:

- "Reliable Circuits Using Less Reliable Relays"

- von Neumann, 1956:

- "Probabilistic Logic and the Synthesis of Reliable Organisms from Unreliable Components"

- Self-checking circuits (1970s)

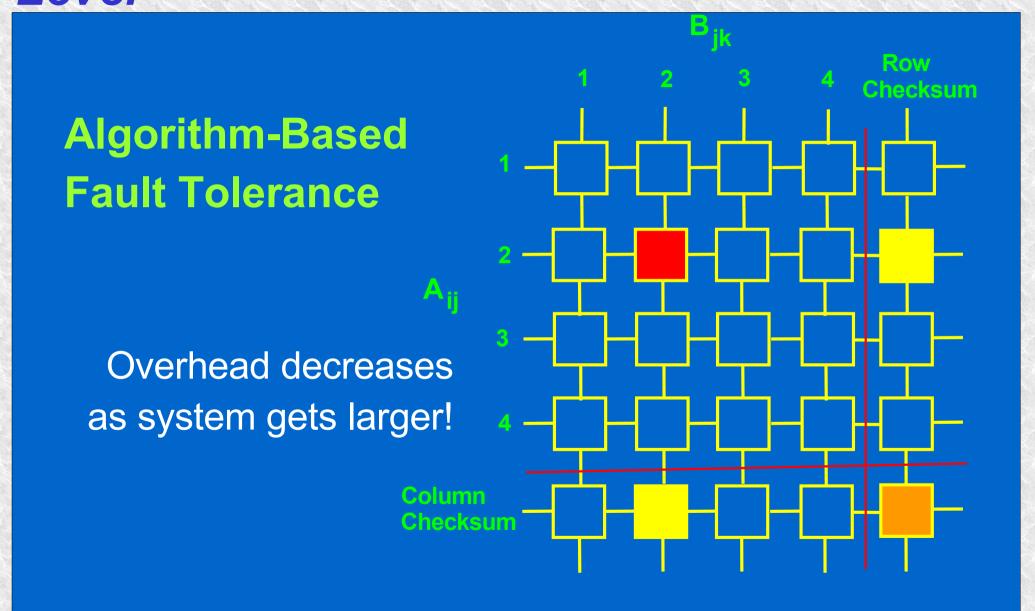

- Algorithm-based fault tolerance (1980s)

- Software-based checks (control flow checks, etc.) (1980s)

## Redundancy at Different Levels

## Protecting Computations at the System Level

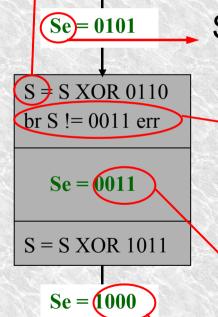

## **CEDA:** Control-flow Error Detection through Assertions (Integrated with GCC)

S: global runtime signature register

- updated at the beginning and end of each node

- each update either an XOR or an AND operation

- op. performed based on the program graph properties

Se: expected value of S at each point in the program - calculated at compile time

Check point: S is checked against its expected value - detects CFE if one occurred

- not required inside every node

Node signature: expected value of S inside a node

Node exit signature: expected value of S immediately after exiting a node

## Dealing with Faults

- Increasing possibility of defects

- Defect tolerance key for yield

- Want system to start in a good state

- Cannot produce cost-effective DRAMS without replacing faulty cells with spares

- However, sparing cells is much more difficult for logic (very high cost for multiplexers, routing)

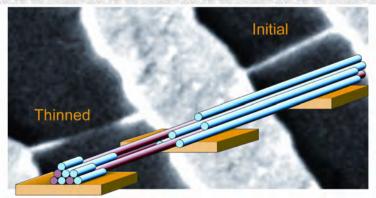

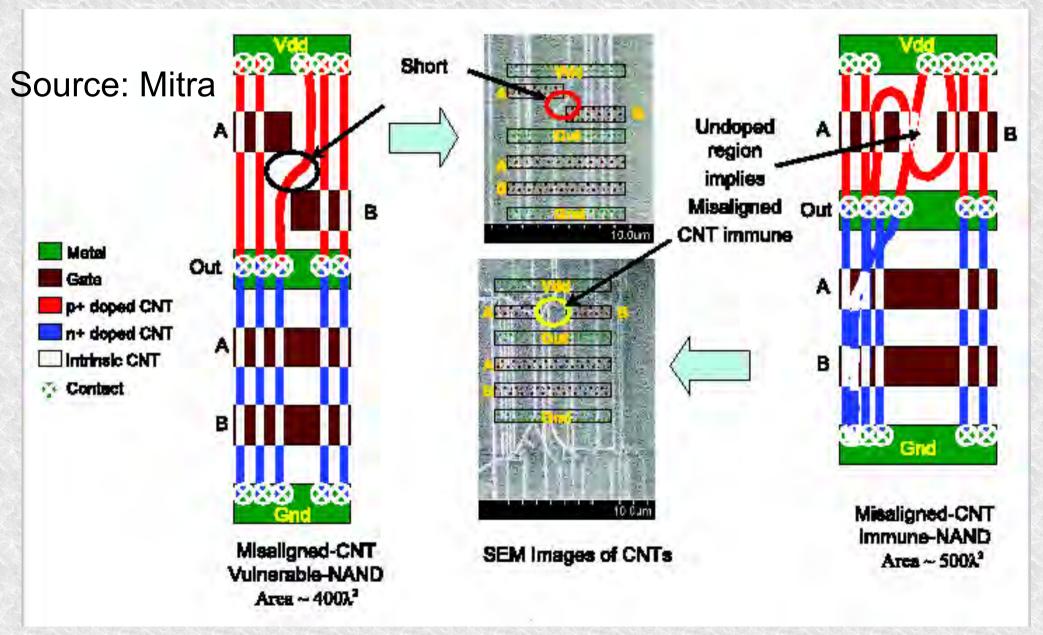

## Defect Tolerance in Carbon Nanotube Circuits

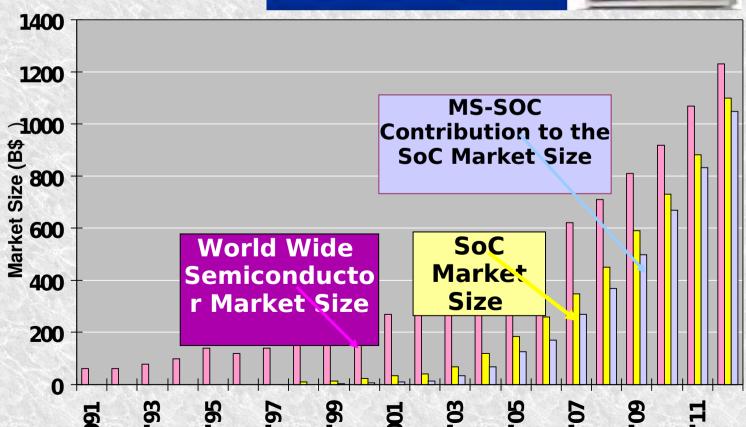

What are some of the characteristics of future products?

Low-cost consumer products

High frequency, high resolution signals

System service (what matters is what customer sees)

Regulations

14

## Objective of dependability

- Guarantee that the system meets customer or regulatory specifications

- Need not check directly for the specifications

- This is becoming impossible to do with low cost

- Only solution for systems of the future is indirect checks from which the specifications can be

inferred accurately

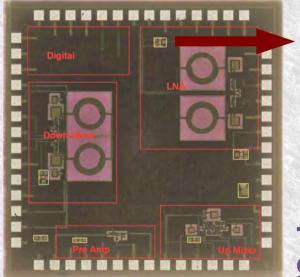

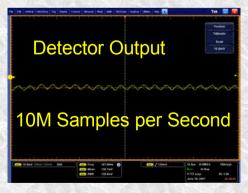

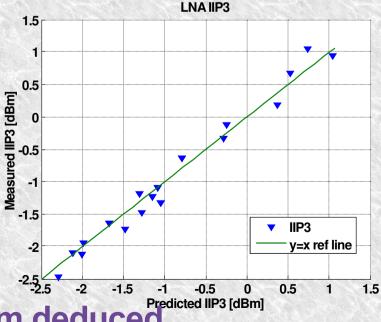

Third harmonic of 2.5.5 2 1.5 1 940 MHz RF system deduced from 10 MS/sec detector output

15

## **Conclusions**

- Need to deal with soft errors (due to variations, etc.)

- Detection and correction techniques

- Tolerate defects in manufacture

- Lots of devices, but efficiently using them is key

- Level to apply solutions?

- Usually higher levels are better

- May find good solutions at low levels, too

- Can utilize many "old" techniques

- Need to look for "new" techniques