Developing Fault Models for Nanowire Logic Circuits

## D. Gil, **D. de Andrés**, J.-C. Ruiz, P. Gil {dgil, ddandres, jcruizg, pgil}@disca.upv.es

- Introduction

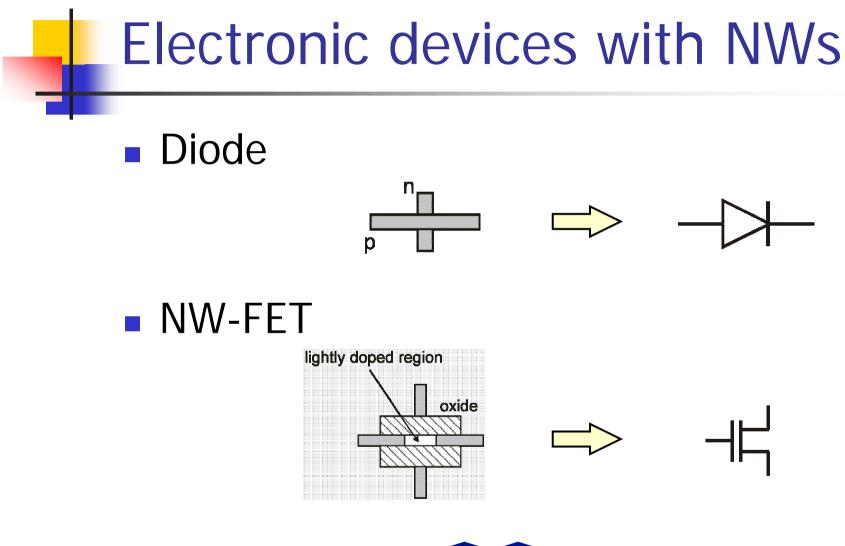

- NW-based logic circuits

- Fault models at device level

- Fault models at logic level

- Conclusions and challenges

#### Introduction

- NW-based logic circuits

- Fault models at device level

- Fault models at logic level

- Conclusions and challenges

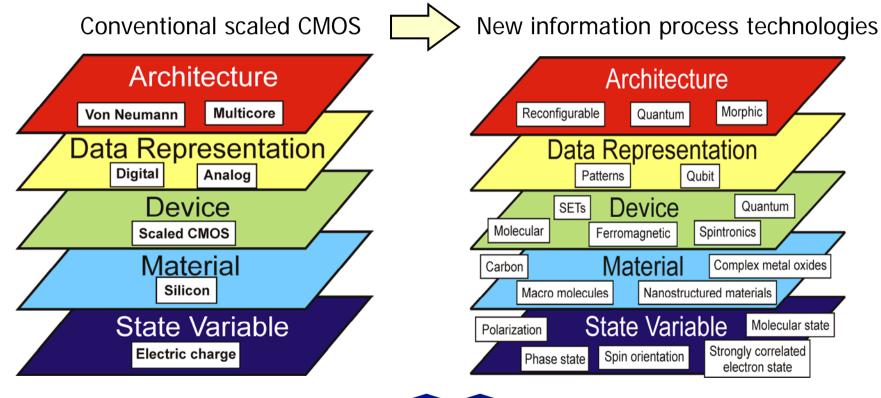

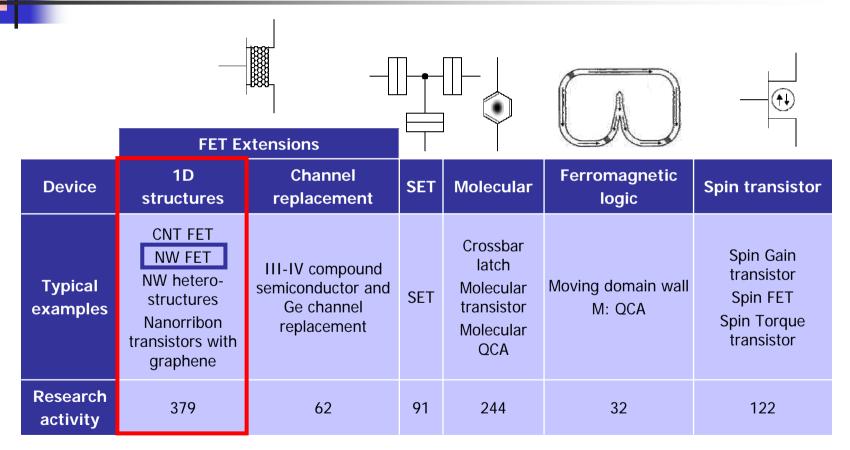

## Emerging research information processing devices

4

## New information process technologies

### Methodology

- Introduction

- NW-based logic circuits

- Fault models at device level

- Fault models at logic level

- Conclusions and challenges

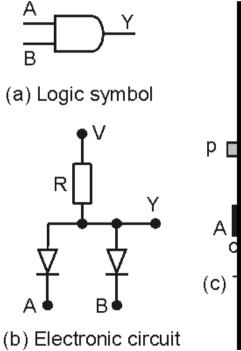

#### NW-based AND gate

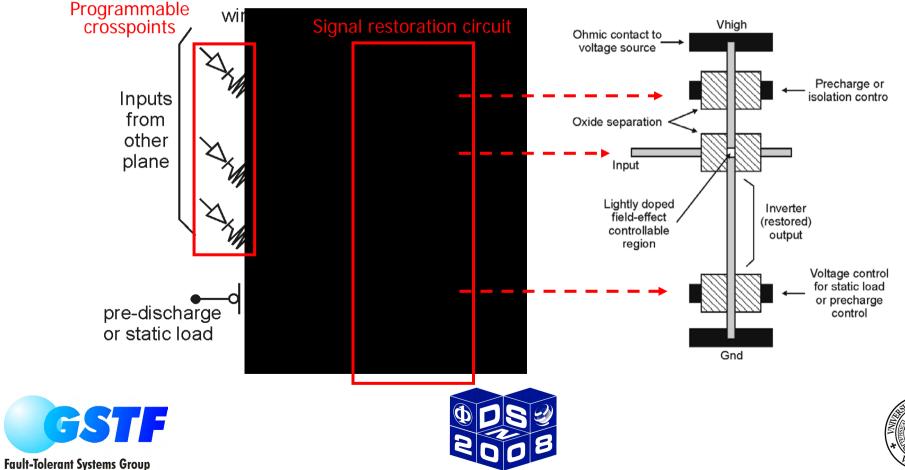

## NW-based OR nanoPLA plane with signal restoration

- Introduction

- NW-based logic circuits

- Fault models at device level

- Fault models at logic level

- Conclusions and challenges

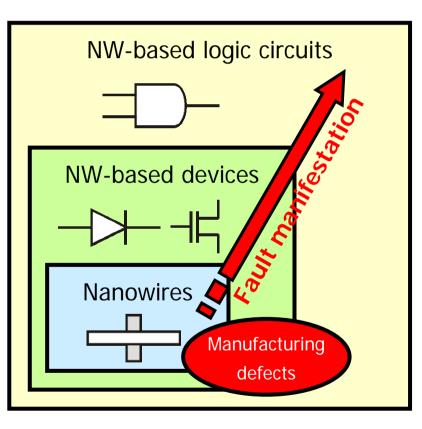

### Manufacturing defects

| Defect                         |                     | Cause/Mechanism                                                     | Effect                                                   |  |

|--------------------------------|---------------------|---------------------------------------------------------------------|----------------------------------------------------------|--|

| Nanowire<br>defects            | Broken              | Mechanical stress during assembly                                   | Open I/O connections, p-n junctions or FET channel       |  |

|                                | Poor<br>contacts    | Statistical number of atomic scale bounds                           | Increase of wire resistance                              |  |

|                                | Doping<br>variation | Statistical doping                                                  | Variation of wire resistance                             |  |

| Crosspoint<br>defects          | Open                | Statistical junction formation                                      | Open in diodes or NWFETs<br>Non-programmable crosspoints |  |

|                                | Short               | with tens of molecules                                              | Short in diodes and NWFETs<br>Shorted crosspoints        |  |

| Bridging of adjacent nanowires |                     | Imperfect planar NW alignment<br>Variations in core shell thickness | Shorts between I/O connections or device terminals       |  |

## Fault models at device level (manufacturing defects)

| Causes and r                      | Fault models at device level  |               |                 |       |

|-----------------------------------|-------------------------------|---------------|-----------------|-------|

| (manufactur                       | Diodes                        | FETs          | I/O connections |       |

| Nanowire defects                  | Broken wires                  | open          | open            | open  |

|                                   | Poor contacts                 | delay         | delay           | delay |

|                                   | Doping variation              | delay         | delay           | delay |

| Crosspoint defects                | Open crosspoint               | open/missing* | open            | -     |

| Crosspoint defects                | Short crosspoint              | short/extra** | short           | -     |

| Dridging of adjacent              | Imperfect alignment           | short         | short           | short |

| Bridging of adjacent<br>nanowires | Shell thickness<br>variations | short         | short           | short |

\* In programmable circuits: missing devices due to permanent off crosspoints \*\* In programmable circuits: extra devices due to permanent on crosspoints

- Introduction

- NW-based logic circuits

- Fault models at device level

- Fault models at logic level

- Conclusions and challenges

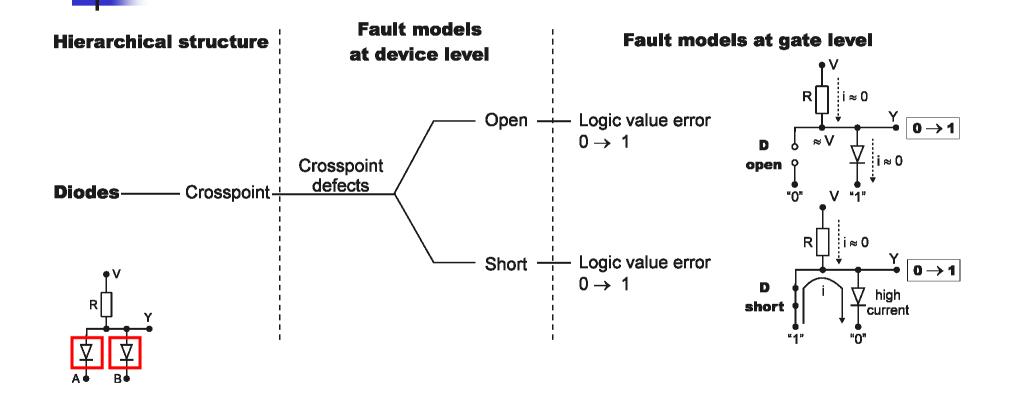

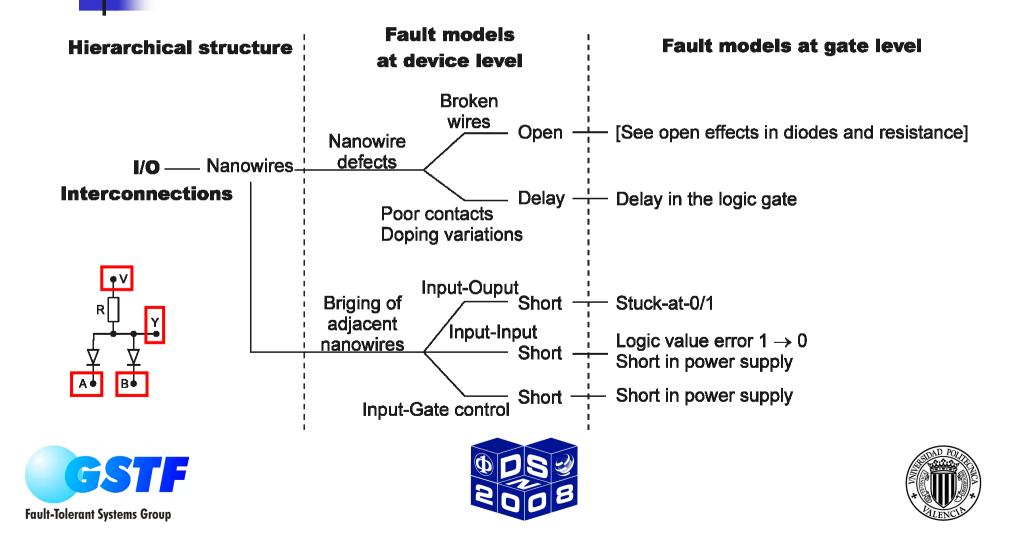

#### Fault models at logic level

- Hierarchical structure

- Logic circuit made of devices made of NWs

- Single faults

- For each *device* in the structure  $\rightarrow$

- For each *fault model* at device level  $\rightarrow$

- Analyse the fault propagation to the circuit's output

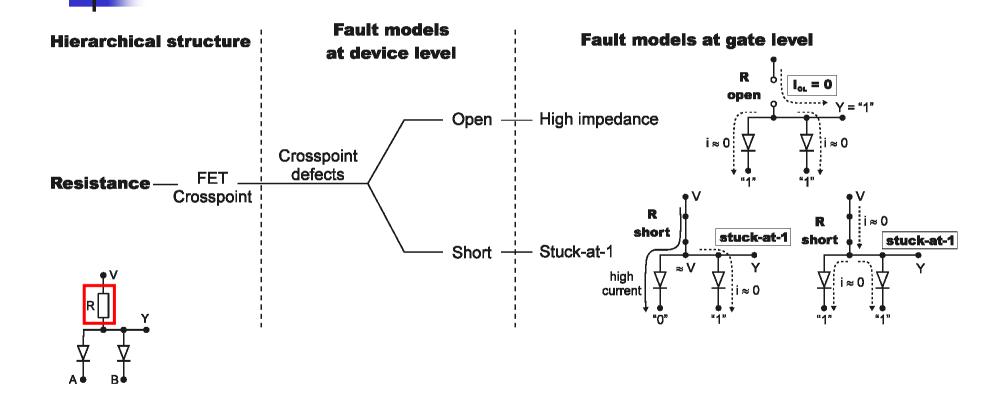

### Fault models at logic level Example 1: AND gate

### Fault models at logic level Example 1: AND gate

### Fault models at logic level Example 1: AND gate

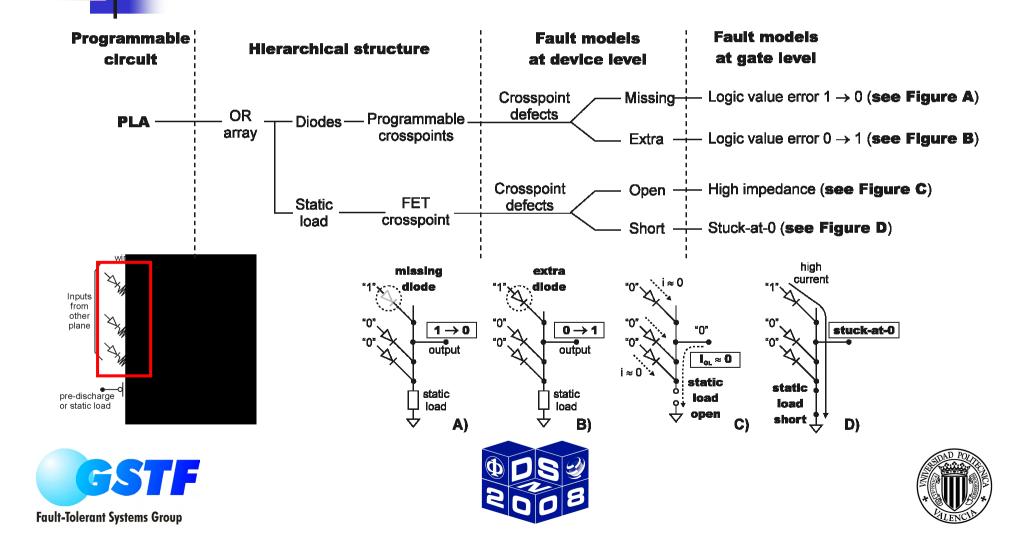

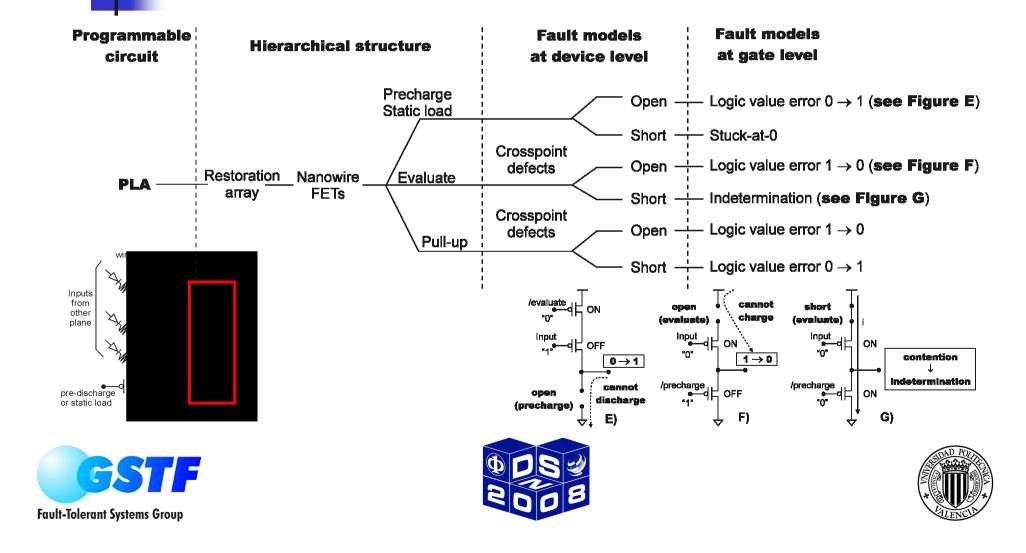

#### Fault models at logic level Example 2: Programmable circuits

#### Fault models at logic level Example 2: Programmable circuits

- Introduction

- NW-based logic circuits

- Fault models at device level

- Fault models at logic level

- Conclusions and challenges

### Conclusions

- Definition of fault models for nanowire-based logic circuits

- Bottom-up methodology

- Physical  $\rightarrow$  Device  $\rightarrow$  Logic

- The methodology can be applied to other nanodevices and architectures

### Challenges

- Modelling a wider set of faults

- Wearout faults

- Transient faults

- Multiple faults

- Fault models for other nanodevices

- CNT, molecular, spintronics, ...

- Dependability assessment of emerging (fault/defect tolerant) nanoarchitectures

# Thank you for paying attention!

Developing Fault Models for Nanowire Logic Circuits

## D. Gil, **D. de Andrés**, J.-C. Ruiz, P. Gil {dgil, ddandres, jcruizg, pgil}@disca.upv.es