## **Trustworthy Critical Infrastructures**

Threats, Challenges, and Countermeasures

### Saman Zonouz

IFIP WG 10.4 - Jan. 2016

### Outline

- Background

- Cyber-physical critical infrastructures

- Potential threats

- Our Solutions

- Trustworthy sensing

- Adaptive intrusion tolerance

- Control command verification

- Other contributions

- Conclusions and Q&A

## Double threatwo fronts

INDUSTRIAL CONTROL SYSTEMS

CYBER EMERGENCY RESPONSE TEAM

#### **CONTENTS**

INCIDENT RESPONSE ACTIVITY

SITUATIONAL AWARENESS

ICS-CERT NEWS

#### **INCIDENT RESPONSE ACTIVITY**

### MALWARE INFECTIONS IN THE CONTROL ENVIRONMENT

ICS-CERT recently provided onsite support at a power generation facility where both common and sophisticated malware had been discovered in the industrial control system environment. The malware was discovered when an employee asked company IT staff to inspect his USB drive after experiencing intermittent issues with the drive's operation. The employee routinely used this USB drive for backing up control systems configurations within the control environment.

When the IT employee inserted the drive into a computer with up-to-date antivirus software, the antivirus software produced three positive hits. Initial analysis caused particular concern when one sample was linked to known sophisticated malware. Following analysis and at the request of the customer, an onsite team was deployed to their facility where the infection occurred.

ICS-CERT's onsite discussions with company personnel revealed a handful of machines

em

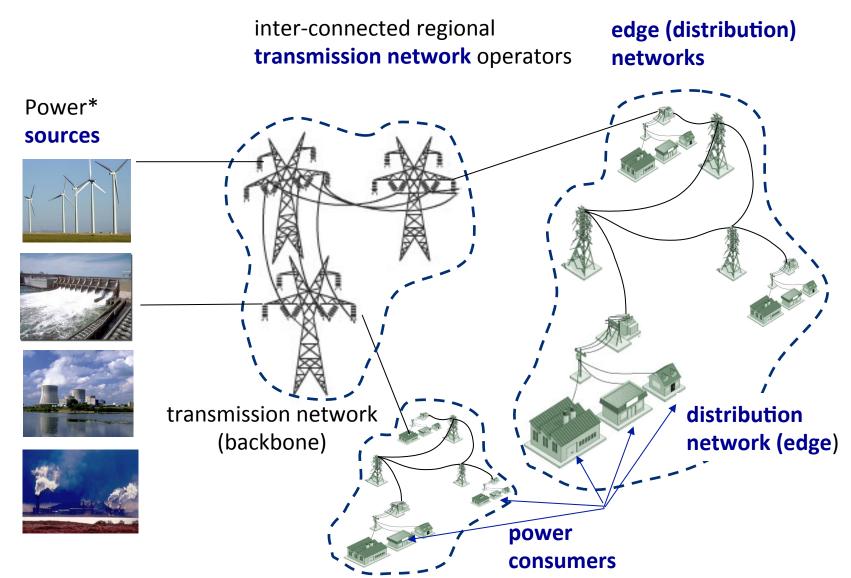

### The Electric Grid Structure

<sup>4</sup>

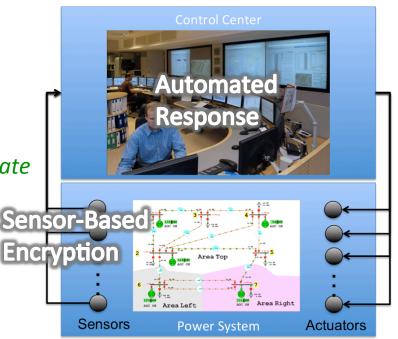

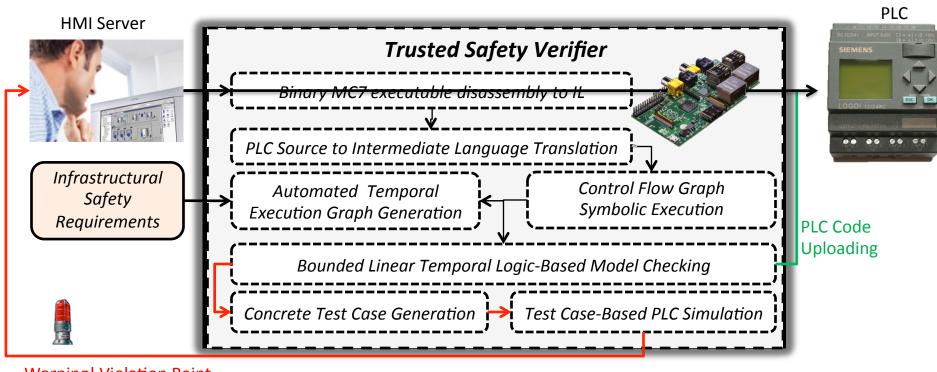

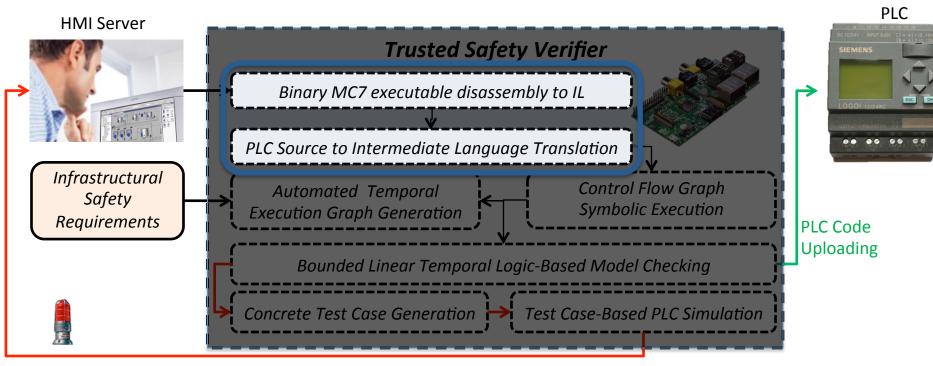

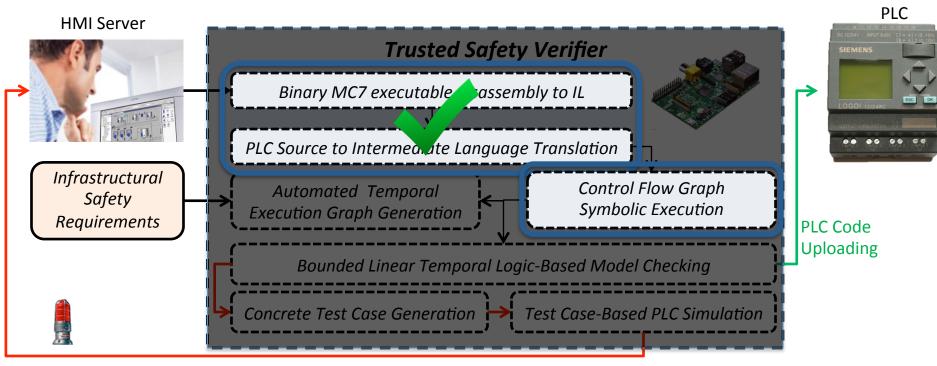

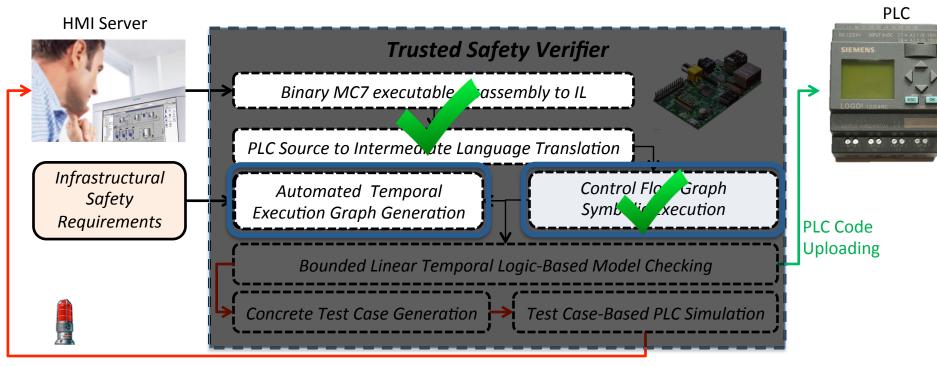

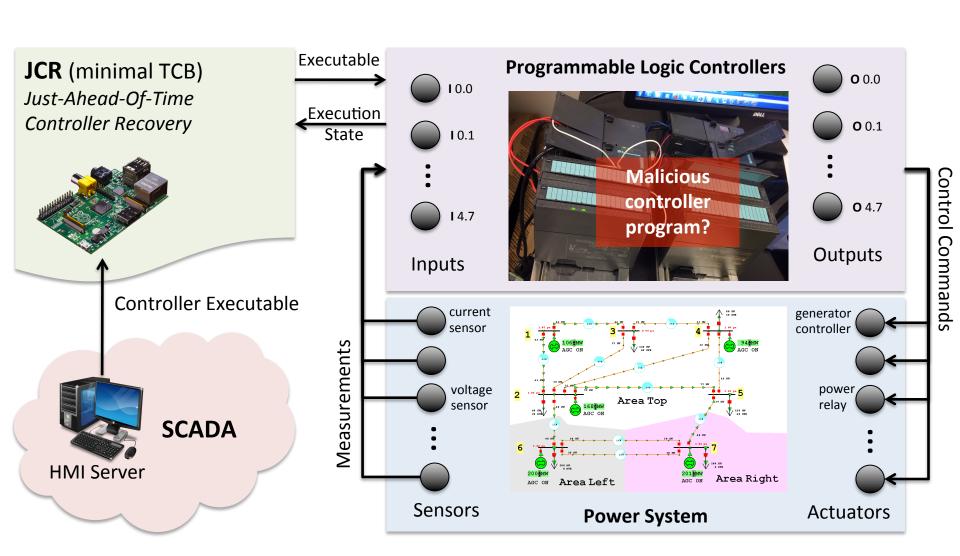

# **Control Command Verification**

- Problem

- Malicious control command injection

- Solution

- Verify if the control command is legitimate

- Challenge

- Not having to check every single input?

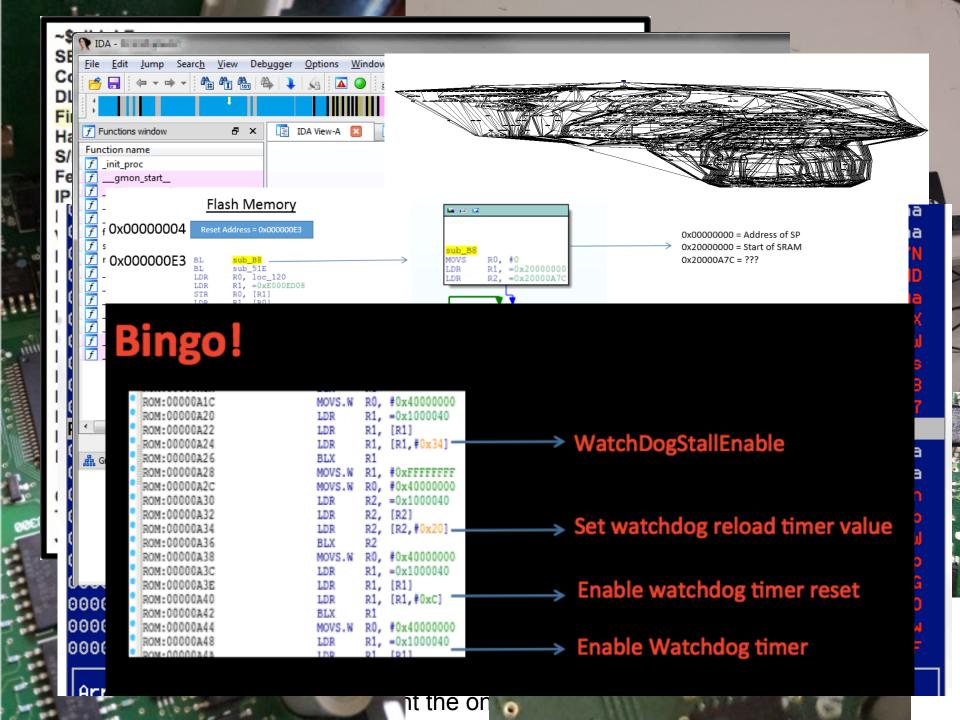

## Binary Executable Disassembly

#### **Binary format (MC7):**

Siemens Machine Code (.mc7)

```

Offset(h) 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

70 70 01 01 01 08 00 01 00 00 01 B2 00 00 00 00

03 41 <u>0F C9</u> ZA 4A 03 A1 63 83 Z1 A7 00 1C 00

00 1A 01 40 C0 01 C0 01 10 09 41 60 00

00000040

00 04 7E 53 00 12 FB 79 00 04 7E 57 00

00000050

84 00 00 00 FB 76 00 04 FE 6B 00 14 FB

00000060

00000070

00000080

10 02 CO 01 10 01 41 60 00 14 FB 70 01 04

00000090

00 02 10 02 CO 01 10 03 41 60 00 18 FB 7C FB 79

0A0000A0

00 01 FE 6F 00 14 FE 0B 84 00 00 00 75 01

000000B0

000000C0

000000D0

OD0000E0

000000F0

FB 72 01 04 FE 6B 00 14 FB 7C 10 04 C0 01

41 60 00 14 FB 74 00 2B 70 0B 00 02 10 08

00000100

FB 71 01 04 70 0B 00 02 C0 01 55 01 C0

00000120

00000130

CO 01 FB 73 01 04 CO 01 3D 01 70 0B 00

3D 0A 70 0B 00 02 C0 01 FB 70 01 04 70

CO 01 CO 01 75 01 CO 01 75 0A CO 01 FB 72

00000150

CO 01 at 00 01 00 00 14 00 00 00 02 05 02 05 02

00000160

00000170

05 00 40 00 9A 00 12 00 28 00 2A 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 01 00 58 2F 00 00 00 00 00 00

000001B0

00 00

```

- Type of Block (OB,FC,FB,SFC,SFB) (always @ 0x05)

- Block Number (always @ 0x06 and 0x07)

- Size of Code + 0x02) (always @ 0x00 and 0x07)

- Code

Number of Network

- Size of Network n°1

- Size of Network n°2

- Size of Network n°3

- Size of Network n°4

Size of Network n°5

#### Source code (IL):

Siemens Instruction List (.il)

#### **PLC Architecture**

- Hierarchical addresses

- Not just integers! Prefixed namespace qualifiers

- Siemens/Allen-Bradley has 1/3 qualifiers

- Multi-indexed memory

- Multiple-size memory

- Addressing word- byte- and bit-level

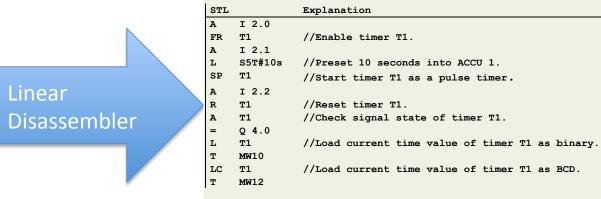

# **IL Source Code Lifting**

#### Source code (IL):

Siemens Instruction List (.il)

```

Explanation

I 2.0

//Enable timer T1.

I 2.1

S5T#10s

//Preset 10 seconds into ACCU 1.

T1

//Start timer T1 as a pulse timer.

I 2.2

T1

//Reset timer T1.

T1

//Check signal state of timer T1.

0 4.0

T1

//Load current time value of timer T1 as binary.

т

MW10

//Load current time value of timer T1 as BCD.

```

#### Why "IL → ILIL"?

- Direct IL analysis is difficult

- IL syntax/semantics vary widely by vendor

- IL instructions have side affects obscuring certain control flows

- ILIL: based on the Vine intermediate language

- Memory, register and address types

#### Intermediate level code (ILIL):

Instruction List Intermediate language (.ilil)

```

0. // Initialize PLC state.

1. mem := \{\} : mem_t(1);

// Main memory.

2. I := 0:

// Input memory qualifier.

3. Q := 1;

// Output memory qualifier.

4. RLO := 1 : reg1_t;

// Boolean accumulator.

5. FC := 0 : reg1_t;

// System status registers.

6. STA := 0 : reg1_t;

7. ...

9. // A I 0.5

10. STA := load(mem, [I::0::0::5]);

11. cjmp FC == 0 : reg1_t,L1,L2;

12. label L1;

13. RLO := STA;

14. label L2;

15. RLO := RLO && STA;

// Side effects.

16. FC := 1 : reg1_t;

17. ...

18.

19. // = Q 0.1

20. STA := RLO;

21. mem := store(mem, [Q::0::0::1], RLO);

22. FC := 0 : reg1_t;

// Side effects.

23. ...

```

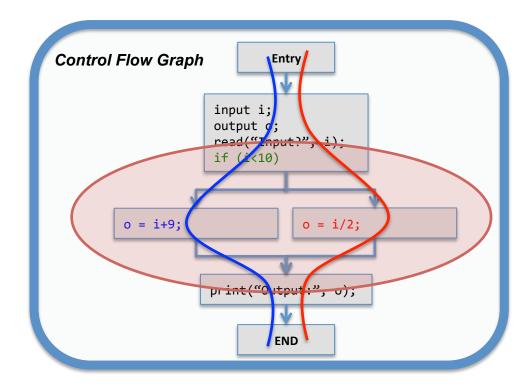

## Symbolic Execution Review

###

#### Concrete execution

Input? ← 16

Output: 8

```

Symbolic execution

Input? ← 'a'

Output:

PC [a<10 ] → a+9

PC [a>=10] → a/2

```

# **ILIL Symbolic Execution**

SE Engine

#### Intermediate level code (ILIL):

Instruction List Intermediate language (.ilil)

```

0. // Initialize PLC state.

// Main memory.

1. mem := \{\} : mem_t(1);

2. I := 0;

// Input memory qualifier.

:= 1;

// Output memory qualifier.

4. RLO := 1 : reg1_t;

// Boolean accumulator.

5. FC := 0 : reg1_t;

// System status registers.

6. STA := 0 : reg1_t;

9. // A I 0.5

10. STA := load(mem, [I::0::0::5]);

11. cjmp FC == 0 : reg1_t,L1,L2;

12. label L1;

13. RLO := STA;

14. label L2;

15. RLO := RLO && STA;

16. FC := 1 : reg1_t;

// Side effects.

17. ...

18.

19. // = Q 0.1

20. STA := RLO;

21. mem := store(mem, [Q::0::0::1], RLO);

22. FC := 0 : reg1_t;

// Side effects.

23. ...

```

#### **Symbolic Scan Cycle:**

(Path condition, symbolic output)

```

Input ← 'a'

Output:

PC [a<10 ] → a+9

PC [a>=10] → a/2

```

- Control flow graph exploration

- SMT solver for predicate feasibility checking

- E.g., is "(a<10) && (20<a)" satisfiable?

- Optimizations

- Bounded loop execution (quaranteed correctness)

- Indirect function calls w/ symbolic address values

- Opcode-based register type inference

- Symbolic execution covers a "single" scan cycle

- Subsequent IO scans are treated independently

- No temporal considerations, e.g., timers/counters

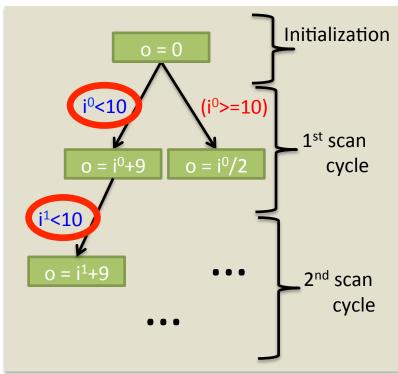

## **Temporal Execution Graph**

#### **Symbolic Scan Cycle:**

(Path condition, symbolic output)

```

Input ← 'a'

Output:

PC [a<10] → a+9

PC [a>=10] → a/2

```

- State based model

- Transitions denote new cycles

- Each state store symbolic memory values

- TEG captures inter-cycle dependencies

- E.g., timers and counters

- Recursive TEG generation return conditions

- Ideal: all states are generated

- Bounded: finite scan-cycle exploration

#### Temporal Execution Graph (TEG):

State notion: symbolic variable vales

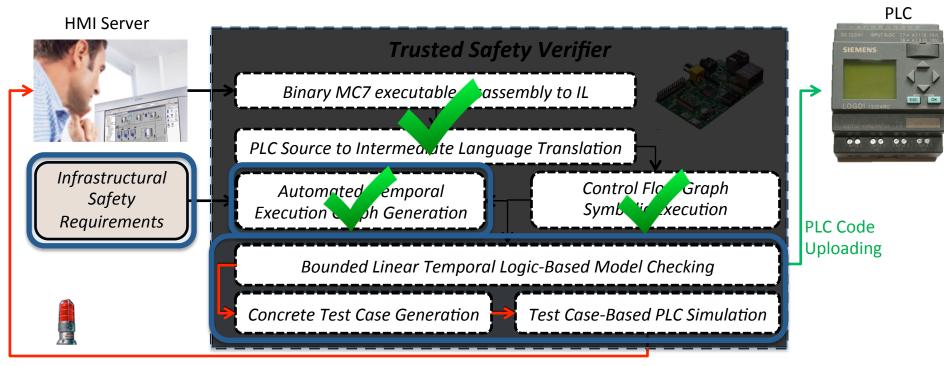

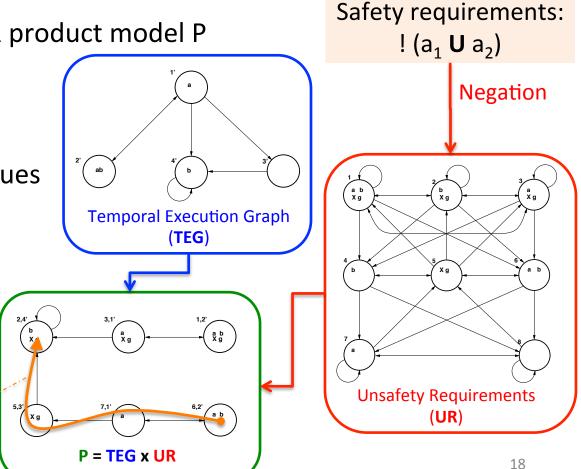

## Infrastructural Safety Requirements

Formulated using linear temporal logic expressions

- Example safety requirement

- English expression

- Relay  $R_1$  should **NOT** open **UNTIL** Generator  $G_2$  turns on

- Logical expression

- Atomic propositions

- a<sub>1</sub>: "Relay R<sub>1</sub> is open"

- a<sub>2</sub>: "Generator G<sub>2</sub> is on"

LTL: !a<sub>1</sub> U a<sub>2</sub>

### Formal Verification

- 1. Negate the LTL Spec formula

- Generates the TEG-UR product model P

- 3. Search for a path in P

- 4. Get concrete input values

### Req-violating input vector:

$$(i^0, i^1, i^2) = (10, 2, 15)$$

Req-violating path condition:

$(i^0 < 12) \& (0 < i^1) \& (i^2 < 20)$

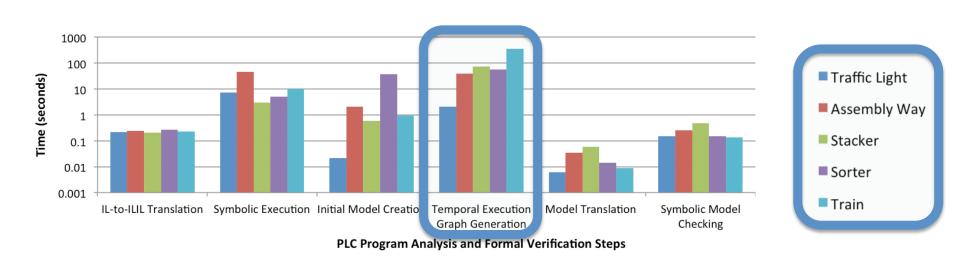

### **Evaluations**

- Implementations

- >30K LOC

- C/C++

- Experimental setup

- Raspberry Pi Linux 3.2.27

- Desktop Ubuntu; 8 GB RAM; Linux 3.5

- Case studies

- Five real Siemens PLC controller programs

- Traffic light, Rail Inter-locking, Assembly line, Stacker, Sorter

## **Detailed Performance Analysis**

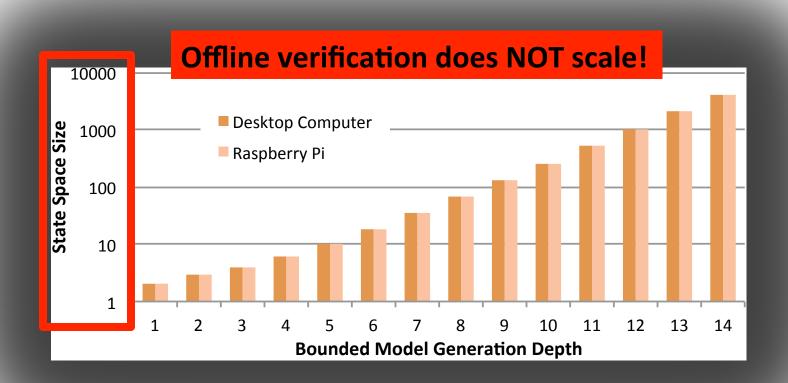

# **Practical Feasibility**

### **Practical Solution?**

#### **Past Work**

Offline formal verification and model checking

- Unscalable for large-scale platforms

Runtime monitoring and intrusion detection

- Too late for effective response and recovery

### **Our Solution**

**Just-Ahead-Of-Time Verification and Response**

- + Remarkably smaller system models to analyze

- + Sufficient time for timely intrusion tolerance

## Just-Ahead-Of-Time Verification

## Generator Reverse Engineering

## Acknowledgements

Collaborators

Sponsors

### Conclusions

- Optimal control vs. safety redlines

- reject the control that violate the power system safety requirements

- replace them with security/safety-preserving countermeasures

- Minimal trusted computing base for infrastructural resilience

- easier to analyze, verify its correctness, and protect its cyber-security

- guarantee safety while "huge" SCADA solves for the optimal plant control

- JAT verification allows for countermeasure selection

- proactive tolerance to prevent too-late responses

- learns decided-upon responses for later similar unsafe states

Thank You!